TTLの論理ゲート

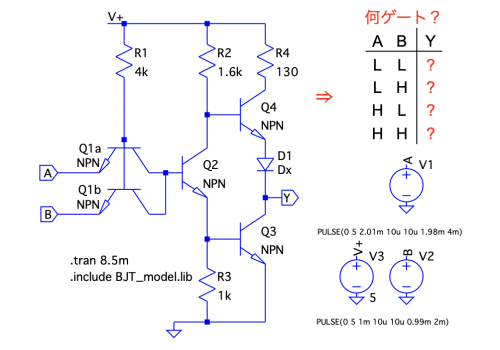

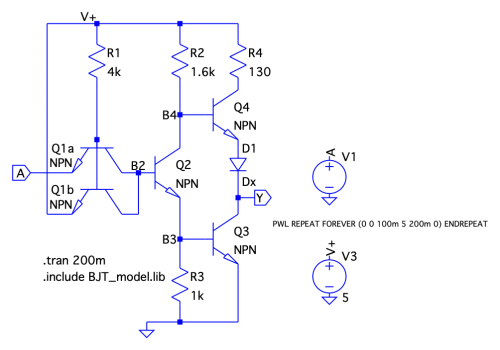

図1は,TTL(トランジスタ・トランジスタ・ロジック)の内部等価回路で,AとBが2つの入力,Yが出力になる論理ゲートです.TTLは0Vがディジタル信号の"L"(Low),5Vがディジタル信号の"H"(High)に相当します.信号の組み合わせは4通りになり,その論理演算がYに現れます.4通りの信号が加わったときの論理演算から,図1は,(a)~(d)の何論理ゲートでしょうか.

(a)ANDゲート (b)NANDゲート (c)ORゲート (d)NORゲート

Q1a,Q1bは,エミッタ端子が複数あるマルチエミッタ・トランジスタと呼ばれます.このマルチエミッタ・トランジスタを分解して,PN接合のダイオードに置き換えると回路が分かりやすくなります.置き換えた回路で4通りの信号のときYの論理(0Vあるいは5V)を検討すると分かります.

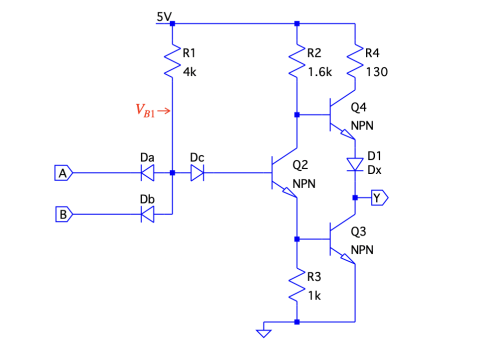

図2は,図1のマルチエミッタ・トランジスタをダイオードに置き換えた回路です.マルチエミッタ・トランジスタは,NPNトランジスタなので,ベースがP型,エミッタとコレクタがN型の半導体です.これをダイオードに置き換えると,図2のようにP型のアノードが共通でR1に繋がり,N型のカソードがA,B,Q2ベースに繋がる3つのダイオード(Da,Db,Dc)になります.ダイオードは,アノードの電圧がカソードの電圧より約0.7V高いときにONとなり,電流がアノードからカソードに流れます.その逆で,アノードの電圧がカソードより低いときや等しいときはOFFとなって電流は流れません.このようにダイオードは,アノードとカソードに掛かる電圧により,一方向にしか電流を流さないスイッチになります.

次にQ2がONからOFFになる切り替えは,Da,Db,Dcのアノードの電圧(VB1)で決まります.具体的には,Q2とQ3のベース・エミッタ電圧約0.7VとDcの順方向電圧約0.7Vを加えた約2.1V付近がしきい値となります.これらをAとBの4条件に当てはめて,回路の動きを検討します.

Da,Db,Dcが置き換えたダイオード.

「Aが"L",Bが"L"」のとき,Da,Dbのカソードの両方が0Vとなります.このときダイオードのアノードの電圧は,カソードの電圧より高い状態となり,DaとDbが,ONとなります.これにより,Da,Db,Dcのアノードの電圧(VB1)は,約0.7Vとなり,Q2がONになるVB1のしきい値約2.1Vより低いため,Q2とQ3がOFF,Q4がONとなります.よって,Yの電圧は,5Vとなり,ディジタル信号(Y)は"H"となります.

「Aが"L",Bが"H"」のとき,Daはカソードが0VでONとなります.Dbはカソードが5VなのでOFFです.Da,Db,Dcのアノードの電圧は,DaがONしているので約0.7Vとなり,Q2がONになるVB1のしきい値約2.1Vより低いため,Q2とQ3がOFF,Q4がONとなります.よって,Yの電圧は,5Vとなり,ディジタル信号(Y)は"H"となります.

「Aが"H",Bが"L"」のとき,Daのカソードが5VでOFFとなります.,Dbはカソードが0VなのでONです.Da,Db,Dcのアノードの電圧は,DbがONしているので約0.7Vとなり,Q2がONになるVB1のしきい値約2.1Vより低いため,Q2とQ3がOFF,Q4がONとなります.よって,Yの電圧は,5Vとなり,ディジタル信号(Y)は"H"となります.

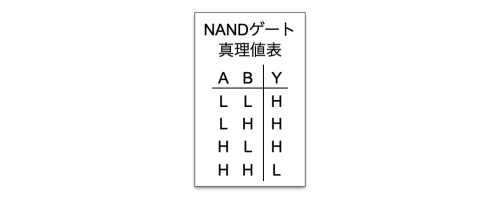

「Aが"H",Bが"H"」のとき,Da,Dbのカソードの両方が5Vとなります.Da,DbはOFFとなります.これにより,電源の5VからR1とDcを通ってベース電流が流れてQ2とQ3はON,Q4がOFFとなります.Yの電圧はトランジスタの飽和電圧まで低くなり,ほぼ0Vとなります.よって,ディジタル信号(Y)は"L"となります.この検討結果を表1の真理値表に示します.この真理値になるのは(b)のNANDゲートになります.

この真理値はNANDゲートになる.

●NANDゲートの内部回路

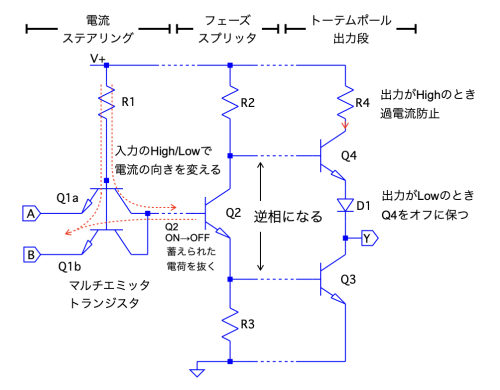

図3は,図1のTTLのNANDゲートを3ブロックに分けて解説を加えました.NANDゲートは,R1,Q1a,Q1bからなる電流ステアリング回路,Q2,R2,R3からなるフェーズ・スプリッタ回路,Q3,Q4,D1,R4からなるトーテム・ポール出力段で構成しています.

TTLは3段構成になっている.

初段の電流ステアリングは,AとBの"H"または"L"の状態により,電流の経路を変えて,後段のQ2をON/OFFします.先程の真理値表の検討の通り,AとBの両方が"H"のとき,Q2のベースに電流が流れます.AとBの片方または両方が"L"のとき,Q2のベースに電流は流れません.

フェーズ・スプリッタは,Q2のON/OFFにより,コレクタ側の電圧とエミッタ側の電圧が逆相になる信号を生成します.位相が異なる2つの信号は,トーテム・ポール出力段の入力になり,Q3とQ4を交互にON/OFFさせます.フェーズ・スプリッタについては過去のメルマが「1つの入力から同相と逆相の2つの出力を作る」で解説していますので,そちらも参照してください.

トーテム・ポール出力段は,出力(Y)に繋がる重い負荷に対し,出力が"H"のときはQ4から電流を吐き出し,その逆に,出力が"L"のときはQ3が電流を吸い込みます.ダイオードD1は,出力が"L"のときにQ4をOFFに保つためのダイオードです.R4は出力が"H"のときに,電源からQ4を通って出力に流れる電流を制限して過電流にならないようにする抵抗です.

TTLのスイッチング・スピードは,トランジスタが飽和したときのベースに蓄えられた電荷を放電する回復時間で決まります.2つの入力が"H"のときはQ2がONしてトランジスタは飽和しており,ベースには電荷が蓄積されています.どちらかの入力が"L"に切り替わると,ベースに蓄積された電荷をQ1aまたはQ1bのコレクタから抜き取るので回復時間が短くなって高速動作をします.他の対策として,高速スイッチングをさせるため,製造プロセスでシリコンへ金をドープします.金をドープしたトランジスタは,ベースとコレクタ領域にある少数キャリアを再結合させ,蓄えられる電荷が少なくなるので,スイッチングが速くなります.反面,金をドープしたトランジスタは電流増幅率が小さくなる欠点もあります.

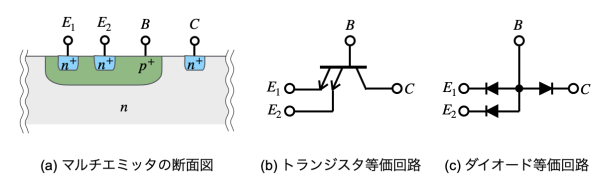

●1つのNPNにエミッタが複数あるマルチエミッタ

初段の電流ステアリングにあるQ1aとQ1bはマルチエミッタ・トランジスタです.この素子の断面図を図4(a)に示します.図1と図3では,2つのトランジスタ(Q1aとQ1b)で表していますが,実際は図4(a)のように1つのNPNトランジスタに2つのエミッタがあるデバイスになります.図4(b)はマルチエミッタ・トランジスタをトランジスタの記号で表した等価回路です.文献などに載っている回路図記号は図4(b)が使われています.図4(c)はダイオードで表した等価回路図です.先程の図2の検討では図4(c)を用いました.

●NANDゲートの真理値をシミュレーション

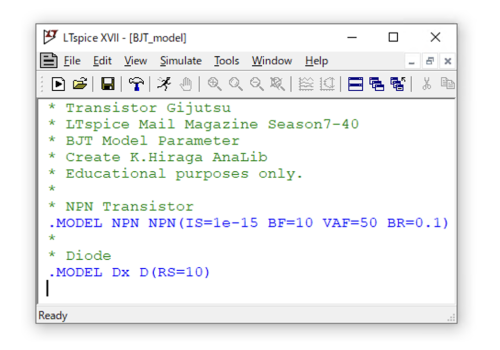

ここでは,図1のNANDゲートの真理値をシミュレーションで確かめて答え合わせをします.AとBにはV1とV2の信号源で矩形波を入力し,表1の真理値表にある"H"と"L"の4通りを加えます.シミュレーションはドット・コマンドの「.tran 8.5m」を指定し,0ms~8.5ms間のトランジェント解析を実行します.トランジスタのモデルパラメータは,「.include BJT_model.lib」のコマンドで,図5に示したモデル・ファイルを読み込みます.図5では,NPNトランジスタのベース・エミッタ間の逆方向飽和電流は「IS=1×10-15A」,順方向の電流増幅率は「BF=10」,順方向のアーリ電圧は「VA=50V」,逆方向の電流増幅率は「BR=0.1」,ダイオードの抵抗は「RS=10Ω」で与えます.

「.include」コマンドでBJT_model.libを読み込む.

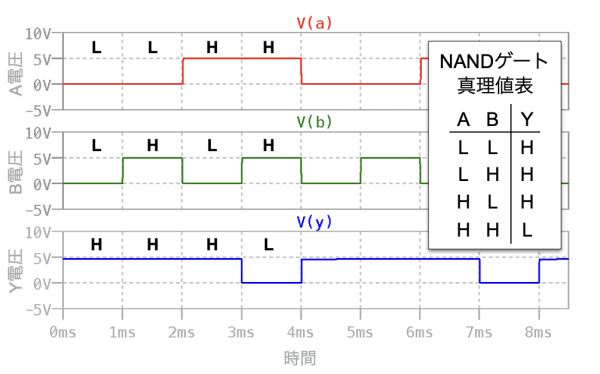

図6は,シミュレーション後のプロットです.上段がAの入力波形,中段がBの入力波形,下段がYの出力波形です.このように4通りの入力の真理値を調べるとNANDゲートになります.

NANDゲートの真理値になるのが分かる.

●スタンダードTTLの入出力電流について

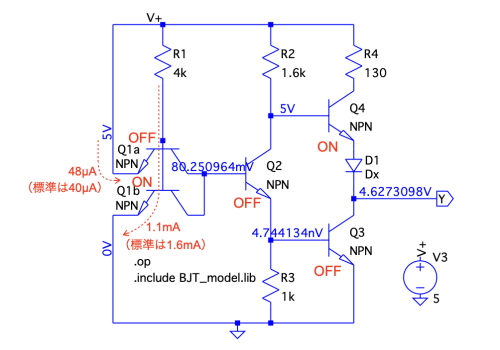

図7は,出力Yが"H"になる「Aが"H",Bが"L"」のときの直流動作点をドット・コマンドの「.op」を用いて調べた結果で,入力電流をテキストで加えました.この結果を用いて,スタンダードTTLの入出力電流について検討します.

図7より,スタンダードTTLは,入力が"H"になる端子は,Q1aに流れる電流のように48μA(規格では標準で40μA)が流れます.この電流は,Q1aの逆方向の電流増幅率「BR=0.1」でエミッタからコレクタへ流れる電流になります.反対に入力が"L"になる端子は,Q1bに流れる電流のように1.1mA(規格では標準で1.6mA)が流れます.この電流は電源からR1を通りQ1bのエミッタに流れます.この2つの電流があるので,入力端子に"H"または"L"の論理レベルを与えるときは,前段のゲート(または他の回路)は,後段の入力端子の電流を吐き出したり,または吸い込んだりしても"H"または"L"を維持する電流能力が必要になります.

スタンダードTTLでは,1つの出力に最大10個のゲートを接続できるので,出力Yの吐き出し電流は標準で「40μA×10=400μA」,吸い込み電流は「1.6mA×10=16mA」の規格になります.

入力が"H"のときは48μA,"L"のときは1.1mAが流れる.

●スタンダードTTLの入出力伝達特性

図8は,図1の入力Bを"H"の電源(V+)に繋いで固定し,入力をAのみにした回路です.表1の真理値表より,入力Aと出力Yは論理が反転するインバータになります.ここでは図8を使って入出力伝達特性をシミュレーションし,スタンダードTTLの入力レベルと出力レベルについて検討します.シミュレーションは入力Aへ周波数が5Hz,振幅が5Vの三角波を加え,出力Yまでの入出力特性をトランジェント解析で調べます.

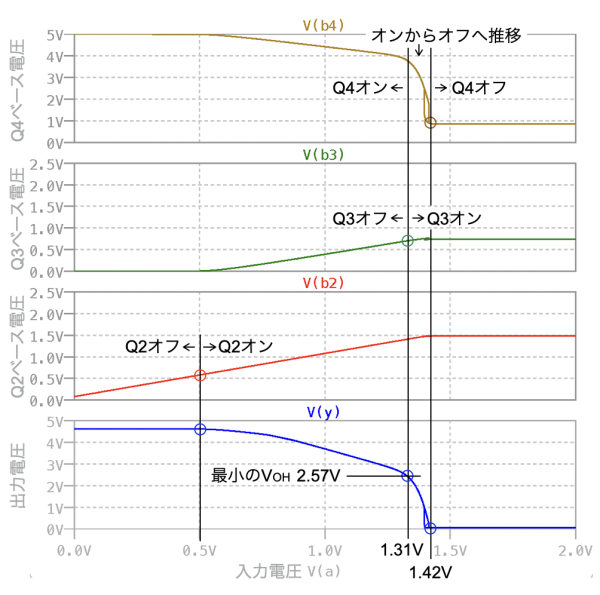

図9は,図8のシミュレーション結果で,Q2,Q3,Q4の3つのベース電圧と出力Yの電圧をプロットしました.入出力特性を調べるため,X軸は時間軸から入力Aの電圧へ変えたプロットになります.図9の最下段にある出力Yのプロットを見ると,入力電圧のある点で出力Yが急峻に切り替わるのではなく,緩やかに出力Yは推移します.これは入力電圧が0Vから徐々に高くなると,0.5VでQ2がONになり,続いて1.31VでQ3がONになります.その後,Q4がONからOFFになるので,緩やかな切り替わりになっています.

図10は,図9の出力電圧のみを図示したNANDの入出力特性です.X軸の下とY軸の左には,スタンダードTTLの入力レベルと出力レベルの規格を図示しました.不定は"H"または"L"が定まらない範囲です.図10より,スタンダードTTLは,電源が5Vのとき中点付近に"H"と"L"の境界があるわけではなく,低い電圧の方にシフトする特性になります.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice7_040.zip

●データ・ファイル内容

TTL NAND.asc:図1の回路

TTL NAND.plt:図1のプロットを指定するファイル

TTL NAND Output High.asc:図7の回路

Transfer characteristic.asc:図8の回路

Transfer characteristic.plt:図8のプロットを指定するファイル

BJT_model.lib:BJTのモデルファイル

■LTspice関連リンク先

(01) LTspice ダウンロード先

(02) LTspice Users Club

(03) トランジスタ技術公式サイト LTspiceの部屋はこちら

(04) LTspice メール・マガジン全アーカイブs

(05) ◆LTspice電子回路マラソン・アーカイブs

(06) ◆LTspiceアナログ電子回路入門アーカイブs

(07) ◆LTspice電源&アナログ回路入門アーカイブs

(08) ◆IoT時代のLTspiceアナログ回路入門アーカイブs

(09) ◆オームの法則から学ぶLTspiceアナログ回路入門アーカイブs

(10) ◆LTspiceエデュケーショナル・ファイルで学ぶアナログ回路アーカイブs